Downloads

Abstract

In this paper, a single-precision floating-point FFT twiddle factor (TF) implementation is proposed. The architecture is based on the Adaptive Angle Recoding CORDIC (AARC) algorithm. The TF design was built and verified on Altera Stratix IV FPGA chip and 65nm SOTB synthesis. The FPGA implementation had 103.9 MHz maximum frequency, throughput result of 16.966 Mega-Sample per second (MSps), and resources utilization of 7.747 ALUTs and 625 registers. On the other hand, the SOTB synthesis has 16.858 standard cells on an area of 298x291 μm2, 166 MHz maximum frequency, and the speed of 27.107 MSps. The accuracy results were 1.133E-10 Mean-Square-Error (MSE) and about 26 part-per-million (ppm) maximum error.

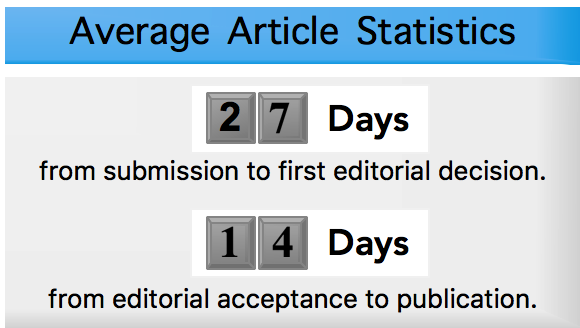

Issue: Vol 1 No T4 (2017)

Page No.: 187-196

Published: Dec 31, 2017

Section: Original Research

DOI: https://doi.org/10.32508/stdjns.v1iT4.468

Download PDF = 436 times

Total = 436 times

Most read articles by the same author(s)

- Quynh Thi Nhu Truong, Thao Thi Phuong Vo, Thuc Trong Hoang, An FPGA-based single-precision floating-point 2048-points FFT implementation based on adaptive angle recoding CORDIC , VNUHCM Journal of Natural Sciences: Vol 1 No T4 (2017)

Open Access

Open Access