Abstract

In this paper, we implement an automatic chip testing system which can be applied on various types of chip packages. The conventional systems, such as manual chip testing systems, often repeat the same steps for input conditions; or high-cost testing systems are designed to be highly optimized, but the installation and operating costs are very expensive. This makes these systems difficult to be applied in education, research or small companies. The automatic chip testing system overcomes the above two weaknesses. The proposed system not only meets the requirement of a basic chip testing process, but also operates automatically and reduces the cost. Users only need to provide input data via a Graphical User Interface (GUI) which is built using C# programming language, then the system will automatically operate and return the corresponding output data to the software to synthesize and compare with the user’s expected data. The hardware is built on the TR4 FPGA Development Kit which helps save the cost of hardware design and its resources. The software and hardware withcommunicate to each other via Universal Asynchronous Receiver-Transmitter (UART) protocol. The proposed system is automatic, optimized and low-cost so that it can be applied both in IC design education and industry.

GIỚI THIỆU

Thiết kế vi mạch ngày càng phát triển và giữ vai trò quan trọng trong sự tiến bộ không ngừng của công nghệ điện tử. Khi nhu cầu sản xuất chip ngày càng cao, hàng loạt các loại chip tối ưu về thời gian, công suất, giá thành và công nghệ ra đời thì yêu cầu kiểm tra những sản phẩm chip cũng ngày càng tăng cao. Do đó, việc xây dựng một hệ thống test chip tự động giữ một vai trò cực kì quan trọng. Lý do thứ nhất là hệ thống này giúp các công ty tiết kiệm chi phí đầu tư vào hệ thống lớn, đó là những hệ thống không cần dùng thường xuyên nhưng chiếm chi phí cao như Advantest 2 , 1 , LTX-Credence 3 , Teradyne 4 . Thứ hai, việc xây dựng hệ thống test chip tự động cũng giảm bớt áp lực cho các công ty về mặt đầu tư nhân sự khi các kỹ sư là những người chuyên thiết kế, không thiên về kiểm tra chip – một công việc chỉ diễn ra khi có sản phẩm chip hoàn thành. Cuối cùng, quy trình test chip thủ công bằng cách đưa từng dữ liệu vào và quan sát kết quả ra tương ứng hiện tại rất mất thời gian, lặp đi lặp lại một số thao tác và quy trình quen thuộc nên cần phải tối ưu quá trình này. Hệ thống test chip tự động tận dụng tài nguyên có sẵn trên Field-Programmable Gate Array (FPGA) để xây dựng quy trình tự động từ việc đưa dữ liệu vào chip đến việc lấy dữ liệu ngõ ra từ chip, sau đó tổng hợp kết quả, so sánh và hiển thị trực quan cho người dùng.

Trong bài báo này, chúng tôi mô tả về một quy trình test chip cơ bản, trình bày hệ thống test chip tự động, và các kết quả thực hiện được.

Phương pháp quy trình test chip cơ bản

Trong quá trình sản xuất chip, giá trị kiểm tra sản phẩm chip chiếm đến 60-70% tổng giá trị dự án (về mặt con người, tính toán và thời gian). Do đó, khi một chip được thiết kế, ngoài việc cân đối giữa các yếu tố về mặt tài nguyên, tốc độ, công suất, giá thành thì khả năng kiểm tra thiết kế cũng là yếu tố cần được cân nhắc và đặt lên hàng đầu.

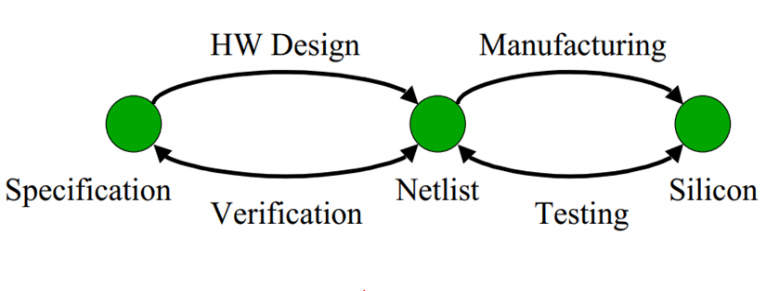

Figure 1 mô tả quá trình kiểm tra thiết kế từ khi có yêu cầu thiết kế đến khi sản xuất và mối tương quan giữa quá trình kiểm tra với quá trình thiết kế 5 .

Quá trình kiểm tra thiết kế gồm 2 bước :

i ) Kiểm tra trong quá trình thiết kế (Verification): Khi thiết kế phần cứng, có thể sử dụng các công cụ phần mềm để kiểm tra độ chính xác ở từng bước thiết kế. Quá trình thực hiện trên phần mềm nên rất tối ưu và tiết kiệm thời gian, công sức. Verification đóng vai trò rất quan trọng vì đảm bảo thiết kế phải hoạt động đúng trên mô phỏng. Nếu mô phỏng bị lỗi, chip chắc chắn sẽ không hoạt động, không cần tốn chi phí sản xuất ra chip.

ii ) Kiểm tra thiết kế sau khi sản xuất (Testing): Quá trình này là kiểm tra tính năng thực của chip. Chip phải được kiểm tra, hoạt động ổn định mới có thể đưa vào ứng dụng. Tuy nhiên, việc kiểm tra hàng loạt các sản phẩm chip cần hệ thống máy móc tự động nên rất tốn kém chi phí.

Một quy trình test chip cơ bản như Figure 2 phải đảm bảo đưa được dữ liệu ngõ vào (các trường hợp muốn kiểm tra) vào chip ứng với những điều kiện hoạt động mong muốn (về thời gian, nhiệt độ, môi trường, điện thế cung cấp…). Sau đó, dữ liệu ngõ ra được thu thập (kết quả trả về tương ứng) để xử lí kết quả. Quy trình này có thể thực hiện bằng cách thêm khối test vào chip, khi chip hoạt động khối này sẽ tự động kiểm tra và báo kết quả về hoặc quy trình test ngoài - kiểm tra hoạt động của từng chip sau khi sản xuất 6 .

Phương pháp xây dựng hệ thống test chip tự động

KẾT QUẢ VÀ THẢO LUẬN

Kết quả thực nghiệm trên TCAM

TCAM (Ternary Content A ddressable Memory) là bộ nhớ được thiết kế bởi công ty TNHH Savarti. Mức điện thế I/O của TCAM là 1,8 V, điện thế hoạt động của lõi là 0,9V. Bộ nhớ TCAM có 44 chân ngõ vào và 18 chân ngõ ra. Để kiểm tra chức năng của TCAM trong thực tế, người dùng cần kiểm tra lên đến 300 véc-tơ ngõ vào. Do đó, quy trình kiểm tra TCAM mất nhiều thời gian.

Việc ứng dụng hệ thống trên TCAM giúp hệ thống chứng minh được các đặc điểm: đáp ứng được nhiều ngõ vào và ngõ ra, số lượng lớn trường hợp cần kiểm tra, điện thế I/O ổn định và quy trình kiểm tra diễn ra hoàn toàn tự động. Đặc biệt, việc hệ thống chạy ổn định, ứng dụng đo chip thực tế có chức năng phức tạp là cơ sở để chứng minh chức năng của hệ thống test chip tự động.

Figure 10 là sơ đồ kết nối chip TCAM với bo mạch FPGA. Bo mạch màu xanh lá bên trái là hệ thống gắn chip TCAM cần kiểm tra tính năng, bo mạch màu xanh dương bên phải là hệ thống test chip tự động. Hai hệ thống kết nối I/O với nhau thông qua IDC Cable 2,54 mm và các xung clock hoạt động được cấp từ FPGA đến TCAM bằng ngõ ra SMA.

Sau khi thực hiện quá trình test với nhiều véc-tơ trên chip TCAM, các dữ liệu trả về hoàn toàn khớp với dữ liệu mong đợi được rút trích từ quá trình mô phỏng. Figure 11 là một ví dụ về so sánh các dữ liệu. Figure 11 (a) là dữ liệu ngõ ra nhận về từ hệ thống test chip tự động. Figure 11 (b) là dữ liệu ngõ ra mong đợi được cung cấp bởi người thiết kế TCAM. Có thể thấy rằng, hai dữ liệu (a) và (b) giống nhau nên kết quả của lần kiểm tra này là chính xác.

Figure 10 . (a) Dữ liệu ngõ ra của hệ thống test chip tự động; (b) Dữ liệu ngõ ra mong đợi từ người dùng.

Kết quả thực nghiệm trên TCAM

TCAM (Ternary Content A ddressable Memory) là bộ nhớ được thiết kế bởi công ty TNHH Savarti. Mức điện thế I/O của TCAM là 1,8 V, điện thế hoạt động của lõi là 0,9V. Bộ nhớ TCAM có 44 chân ngõ vào và 18 chân ngõ ra. Để kiểm tra chức năng của TCAM trong thực tế, người dùng cần kiểm tra lên đến 300 véc-tơ ngõ vào. Do đó, quy trình kiểm tra TCAM mất nhiều thời gian.

Việc ứng dụng hệ thống trên TCAM giúp hệ thống chứng minh được các đặc điểm: đáp ứng được nhiều ngõ vào và ngõ ra, số lượng lớn trường hợp cần kiểm tra, điện thế I/O ổn định và quy trình kiểm tra diễn ra hoàn toàn tự động. Đặc biệt, việc hệ thống chạy ổn định, ứng dụng đo chip thực tế có chức năng phức tạp là cơ sở để chứng minh chức năng của hệ thống test chip tự động.

Figure 10 là sơ đồ kết nối chip TCAM với bo mạch FPGA. Bo mạch màu xanh lá bên trái là hệ thống gắn chip TCAM cần kiểm tra tính năng, bo mạch màu xanh dương bên phải là hệ thống test chip tự động. Hai hệ thống kết nối I/O với nhau thông qua IDC Cable 2,54 mm và các xung clock hoạt động được cấp từ FPGA đến TCAM bằng ngõ ra SMA.

Sau khi thực hiện quá trình test với nhiều véc-tơ trên chip TCAM, các dữ liệu trả về hoàn toàn khớp với dữ liệu mong đợi được rút trích từ quá trình mô phỏng. Figure 11 là một ví dụ về so sánh các dữ liệu. Figure 11 (a) là dữ liệu ngõ ra nhận về từ hệ thống test chip tự động. Figure 11 (b) là dữ liệu ngõ ra mong đợi được cung cấp bởi người thiết kế TCAM. Có thể thấy rằng, hai dữ liệu (a) và (b) giống nhau nên kết quả của lần kiểm tra này là chính xác.

Figure 10 . (a) Dữ liệu ngõ ra của hệ thống test chip tự động; (b) Dữ liệu ngõ ra mong đợi từ người dùng.

Kết quả thực nghiệm trên TCAM

TCAM (Ternary Content A ddressable Memory) là bộ nhớ được thiết kế bởi công ty TNHH Savarti. Mức điện thế I/O của TCAM là 1,8 V, điện thế hoạt động của lõi là 0,9V. Bộ nhớ TCAM có 44 chân ngõ vào và 18 chân ngõ ra. Để kiểm tra chức năng của TCAM trong thực tế, người dùng cần kiểm tra lên đến 300 véc-tơ ngõ vào. Do đó, quy trình kiểm tra TCAM mất nhiều thời gian.

Việc ứng dụng hệ thống trên TCAM giúp hệ thống chứng minh được các đặc điểm: đáp ứng được nhiều ngõ vào và ngõ ra, số lượng lớn trường hợp cần kiểm tra, điện thế I/O ổn định và quy trình kiểm tra diễn ra hoàn toàn tự động. Đặc biệt, việc hệ thống chạy ổn định, ứng dụng đo chip thực tế có chức năng phức tạp là cơ sở để chứng minh chức năng của hệ thống test chip tự động.

Figure 10 là sơ đồ kết nối chip TCAM với bo mạch FPGA. Bo mạch màu xanh lá bên trái là hệ thống gắn chip TCAM cần kiểm tra tính năng, bo mạch màu xanh dương bên phải là hệ thống test chip tự động. Hai hệ thống kết nối I/O với nhau thông qua IDC Cable 2,54 mm và các xung clock hoạt động được cấp từ FPGA đến TCAM bằng ngõ ra SMA.

Sau khi thực hiện quá trình test với nhiều véc-tơ trên chip TCAM, các dữ liệu trả về hoàn toàn khớp với dữ liệu mong đợi được rút trích từ quá trình mô phỏng. Figure 11 là một ví dụ về so sánh các dữ liệu. Figure 11 (a) là dữ liệu ngõ ra nhận về từ hệ thống test chip tự động. Figure 11 (b) là dữ liệu ngõ ra mong đợi được cung cấp bởi người thiết kế TCAM. Có thể thấy rằng, hai dữ liệu (a) và (b) giống nhau nên kết quả của lần kiểm tra này là chính xác.

Figure 10 . (a) Dữ liệu ngõ ra của hệ thống test chip tự động; (b) Dữ liệu ngõ ra mong đợi từ người dùng.

KẾT LUẬN

Chúng tôi đã xây dựng được quy trình test chip tự động ứng dụng trên nhiều loại chip khác nhau. Hệ thống giúp người dùng tiết kiệm chi phí cũng như đơn giản hóa quá trình test chip. Hệ thống hoạt động ổn định trên các chip được kiểm tra với thời gian test nhanh và được xử lí tự động.

So với các hệ thống test chip tự động khác trên thị trường như CTS 2 , hệ thống có ưu điểm là giá thành rẻ, nhỏ gọn nhưng vẫn đáp ứng được các nhu cầu cơ bản của một quy trình test chip (số lượng I/O, số lượng mẫu, tần số hoạt động và mức điện thế I/O).

Tuy nhiên, số lượng dữ liệu xử lí trong một lần kiểm tra chỉ 500 data nên chưa ứng dụng cho chip có tính năng phức tạp. Số lượng clock và độ phân giải của các clock chưa cao nên chưa đáp ứng được nhu cầu xác định chính xác giới hạn hoạt động của chip.

DANH MỤC CÁC TỪ VIẾT TẮT

ATE: Automatic Test Equipment

BIST: Build-In Self-Test

DESLAB: Digital Signal Processing and Embedded Systems Laboratory

DLL: Delay-Locked Loop

FPGA: Field-Programmable Gate Array

FSM: Finite State Machine

GUI: Graphical User Interface

HW: Hardware

MEM: Memory

PLL: Phase-Locked Loop

TCAM: Ternary Content-Addressable Memory

TNHH: Trách Nhiệm Hữu Hạn

UART: Universal Asynchronous Receiver-Transmitter

VCD: Value Change Dump

WPF: Windows Presentation Foundation

XUNG ĐỘT LỢI ÍCH

Các tác giả cam đoan không có xung đột lợi ích trong việc công bố bài báo này.

ĐÓNG GÓP CỦA TÁC GIẢ

Tác giả Trần Thị Thu Trang thực hiện xây dựng hệ thống, triển khai thực tế, kiểm tra hệ thống và viết bản thảo.

Tác giả Diệp Phước Lộc, Phan Vũ Huỳnh Tuấn, Nguyễn Tiến Lộc, Lê Trung Khanh đóng góp trong việc xây dựng hệ thống thực tế, thu thập dữ liệu và góp ý cho bản thảo.

Tác giả Lê Đức Hùng, Huỳnh Quốc Hưng có đóng góp quan trọng từ quá trình lên ý tưởng, định hướng sản phẩm, chỉnh sửa và hoàn thiện bản thảo.

References

- J. Bergeron. Writing Testbenches: Functional Verification of HDL Models Second Edition, Springer. 2003; 1-23.. . ;:. Google Scholar

- Mostardini L., Bacciarelli L., Fanucci L., Bertini L., Tonarelli M., Marinis M. De.. FPGA-based Low-cost Automatic Test Equipment for Digital Integrated Circuits. IEEE International Workshop on Intelligent Data Acquisition and Advanced Computing Systems. Sep. 2009;:32-37. Google Scholar

- Jervan G. “Hybrid Built-In Self-Test and Test Generation Techniques for Digital Systems,” PhD. dissertation, Linköpings universitet, Sweden. . 2005;:. Google Scholar

Open Access

Open Access